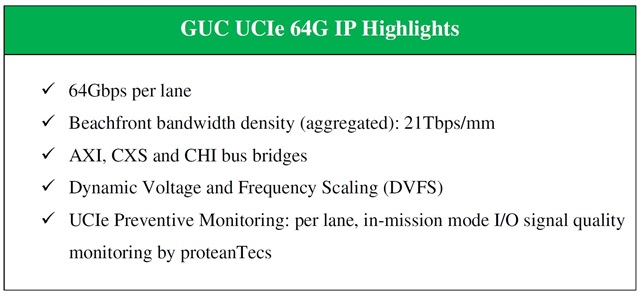

Global Unichip Corp. (GUC), the Advanced ASIC Leader, today announced it has successfully taped-out industry-leading, Universal Chiplet Interconnect Express. (UCIe.) IP, achieving a data rate of 64 Gbps per lane, the highest speed defined in the UCIe specification. The 64G UCIe IP, supporting UCIe 3.0, delivers an impressive bandwidth density of 21 Tbps per 1 mm of die edge (10.5 Tbps/mm full-duplex). This milestone was achieved using TSMC's advanced N3P technology and CoWoS advanced packaging, typically leveraged by AI, high-performance computing (HPC), datacenter and networking applications.

To ensure seamless system integration, GUC has developed bridges for AXI, CXS, and CHI buses utilizing the UCIe Streaming Protocol. These bridges are optimized for high traffic density, low power consumption, minimal data transfer latency, and efficient end-to-end flow control – enabling a seamless transition from traditional single-chip Networks-on-Chip (NoC) to chiplet-based architectures. Additionally, the bridges support Dynamic Voltage and Frequency Scaling (DVFS), allowing real-time voltage and frequency adjustments independently for each die without

interrupting data flow.

GUC's UCIe IP also features advanced reliability capabilities, including UCIe Preventive Monitoring functionality and integrated I/O signal quality monitors from proteanTecs. This technology enables continuous, mission-mode monitoring of signal integrity during data transmission without the need for re-training or disrupting operations. Each signal lane is individually monitored, with real-time detection of power and signal integrity anomalies. Potential defects in bumps and traces are identified early, triggering repair algorithms that replace marginal I/Os with redundant ones to prevent system failures. This proactive approach significantly extends chip lifespan and enhances system reliability.

"We are fully committed to delivering the highest performance and lowest power 2.5D/3D chiplet and HBM interface IPs on TSMC's advanced process and packaging technologies," said Igor Elkanovich, CTO of GUC. "The convergence of 2.5D and 3D packaging technologies, leveraging HBM3E/4/4E, UCIe-A, and UCIe-3D interfaces, enables the development of highly modular processors that exceed reticle size limitations, paving the way for the next generation of highperformance computing. Our strong collaboration with TSMC and its Open Innovation PlatformR (OIP) ecosystem is enabling our customers to accelerate time-to-market in today's AI-driven competitive market."

Click here for more information.

GUC UCIe 64G IP Highlights. Credit:Guc